# H2020-JTI-EuroHPC-2019-1

# **REGALE:** An open architecture to equip next generation HPC applications with exascale capabilities

**Grant Agreement Number: 956560**

#### **D2.3**

# Final integration of sophisticated policies in the REGALE prototype

# **Final**

Version: 1.0

**Author(s):** Pierre-François Dutot, Francesco Antici, Eishi Arima, Andrea Bartolini, Yiannis Georgiou, Mohsen Seyedkazemi Ardebili, Mathieu Stoffel and Nikolaos Triantafyllis

Contributor(s): Lluis Alonso

**Date:** 12.04.2024

# **Project and Deliverable Information Sheet**

|         | Project Ref. №:                      | 956560                    |                                                 |  |  |  |

|---------|--------------------------------------|---------------------------|-------------------------------------------------|--|--|--|

|         | Project Title:                       | REGALE                    |                                                 |  |  |  |

|         | Project Web Site:                    | https://regale-project.eu |                                                 |  |  |  |

|         | Deliverable ID:                      | D2.3                      |                                                 |  |  |  |

| REGALE  | Deliverable Nature: Software         |                           |                                                 |  |  |  |

| Project | Dissemination Lev                    | al. DII *                 | Contractual Date of Delivery:<br>31 / 03 / 2024 |  |  |  |

|         | Dissemination Lev                    | ei. Pu                    | Actual Date of Delivery:                        |  |  |  |

|         |                                      |                           | 12 / 04 / 2024                                  |  |  |  |

|         | EC Project Officer: Evangelos Floros |                           |                                                 |  |  |  |

<sup>\* -</sup> The dissemination levels are indicated as follows: PU = Public, fully open, e.g. web; CO = Confidential, restricted under conditions set out in Model Grant Agreement; CI = Classified, information as referred to in Commission Decision 2001/844/EC.

## **Document Control Sheet**

|            | Title: Final integration of sophisticated policies in the REGALE prototype |                                                                                                                                                                            |  |  |  |  |

|------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|            | ID: D2.3                                                                   |                                                                                                                                                                            |  |  |  |  |

|            | Version: 1.0                                                               | Status: Final                                                                                                                                                              |  |  |  |  |

| Document   | Available at: https://regale-project.eu                                    |                                                                                                                                                                            |  |  |  |  |

|            | Software Tool: Google Docs                                                 |                                                                                                                                                                            |  |  |  |  |

|            | File(s): REGALE_Deliverable_2.3.pdf                                        |                                                                                                                                                                            |  |  |  |  |

|            | Written by:                                                                | Pierre-François Dutot, Francesco Antici,<br>Eishi Arima, Andrea Bartolini, Yiannis<br>Georgiou, Mohsen Seyedkazemi Ardebili,<br>Mathieu Stoffel and Nikolaos Triantafyllis |  |  |  |  |

| Authorship | Contributors:                                                              | Lluis Alonso                                                                                                                                                               |  |  |  |  |

|            | Reviewed by:                                                               | Lluis Alonso, Yiannis Georgiou                                                                                                                                             |  |  |  |  |

|            | Approved by:                                                               | Georgios Goumas                                                                                                                                                            |  |  |  |  |

#### **Document Status Sheet**

| Version | Date       | Status | Comments        |

|---------|------------|--------|-----------------|

| 0.1     | 08.11.2023 | Draft  | Initial version |

| 0.2     | 27.03.2024 | Draft  | Internal review |

| 1.0     | 12.04.2024 | Final  | Corrections     |

# **Document Keywords**

| Vounavede: | REGALE, HPC, Exascale, Sophistications, Performance, Energy |

|------------|-------------------------------------------------------------|

| Keywords:  | Efficiency, Power Constraints                               |

#### **Copyright notice:**

© 2024 REGALE Consortium Partners. All rights reserved. This document is a project document of the REGALE project. All contents are reserved by default and may not be disclosed to third parties without the written consent of the REGALE partners, except as mandated by the European Commission contract 956560 for reviewing and dissemination purposes.

All trademarks and other rights on third party products mentioned in this document are acknowledged as owned by the respective holders.

# **Table of Contents**

| 1 Introduction                                                              | 6  |

|-----------------------------------------------------------------------------|----|

| 2 Performance and Throughput                                                | 9  |

| 2.1 Co-scheduling for throughput and application coupling at the node level | 9  |

| 2.2 Co-scheduling within multicore processing units                         | 18 |

| 2.3 Elastic Resource Management                                             | 23 |

| 2.4 Data-aware resource allocation                                          | 35 |

| 3 Energy Savings                                                            | 46 |

| 3.1 Moldability for energy efficiency                                       | 46 |

| 3.2 ML-based User-Labelling of the Job                                      | 50 |

| 3.3 Integration of ML Models in Production System                           | 51 |

| 3.4 Node level power controls (BDPO)                                        | 57 |

| 3.5 Thermal and Power control on a node level (ControlPULP)                 | 65 |

| 4 Under Power Constraints                                                   | 80 |

| 4.1 System Level Power-Capping with OAR                                     | 80 |

| 4.2 Application level Power-Capping with BEO                                | 86 |

| 5 Combining Sophistications                                                 | 97 |

# **Executive Summary**

This final report details the REGALE project's achievements for optimised energy aware resource utilisation in HPC systems. The sophistications are designed with the project's three key objectives in mind: effective resource utilisation, broad applicability, and user-friendly supercomputing services.

Work Package 2 (WP2) "Sophisticated resource allocation and management" is the key focus of this report. WP2 subtasks explored various aspects, which are presented in this report with three main objectives, improving performance and throughput, providing energy savings, and achieving maximum efficiency under power constraints.

This final report provides a valuable resource for those interested in the REGALE project's achievements and how they contribute to improved resource allocation and management for High-Performance Computing systems.

# **List of Abbreviations and Acronyms**

| Abbreviation / Acronym | Meaning                                 |  |

|------------------------|-----------------------------------------|--|

| AAPC                   | Application Aware Power Capping         |  |

| CPU                    | Central Processing Unit                 |  |

| DVFS                   | Dynamic voltage and frequency scaling   |  |

| EPI                    | European Processor Initiative           |  |

| FW                     | Firmware                                |  |

| GPU                    | Graphical Processing Unit               |  |

| HLC                    | High Level Controller                   |  |

| HPC                    | High Performance Computing              |  |

| HW                     | Hardware                                |  |

| I/O                    | Input/Output                            |  |

| LLC                    | Low Level Controller                    |  |

| ML                     | Machine Learning                        |  |

| MPI                    | Message Passing Interface               |  |

| OS                     | Operating System                        |  |

| OSPM                   | Operating System Power Management       |  |

| PMI                    | Power Management Interface              |  |

| RJMS                   | Resource and Job Management System      |  |

| SCMI                   | System Control and Management Interface |  |

| SPM                    | System Power Manager                    |  |

| SW                     | Software                                |  |

BDPO, BEO, EAR, OAR, Ryax are software names and not acronyms.

#### 1 Introduction

The REGALE project aims to establish an open architecture, propose a prototype software stack, and integrate advancements into various components of the stack to optimize resource utilization. This final report details the project's improvements to its different components throughout its lifecycle.

The report outlines the sophistications developed in relation to the project's three strategic objectives, which can be simply summarized here:

- Strategic Objective 1 (SO1): Effective Resource Utilization

- Improved application performance

- Increased system throughput

- Minimized performance degradation under power constraints

- Decreased energy to solution

- Strategic Objective 2 (SO2): Broad Applicability

- Strategic Objective 3 (SO3): Easy and Flexible Use of Supercomputing Services

For more details on these objectives and for a description of the Regale Architecture, Prototype and Use Cases, readers are invited to read Deliverable 1.3. This report presents the progress made in Work Package 2 (WP2), which concentrates on sophisticated resource allocation and management. The various subtasks within WP2 address distinct aspects of resource allocation, including co-scheduling, moldability, and power management.

As this deliverable is meant for the general public, we will not present a simple collection of tasks, but rather structure the results along three main topics, in connection to the strategic objectives. The first of these topics, detailed in Section 2, is the improvement of application performances, and global throughput (this can be viewed as globally improving the number of jobs per second). The different subsections are different ways to improve this objective.

First, we explore co-scheduling for enhanced throughput and application coupling at the node level. In this, a machine learning-based approach is used to optimize resource allocation in HPC systems by co-scheduling multiple applications with different resource requirements on the same compute nodes. The method also involves determining the most suitable allocation policy (e.g. compact or spread allocation) for each application.

Then, we look at *co-scheduling within multicore processing units*. This subsection details a novel co-scheduling strategy that incorporates machine learning for automated resource allocation in heterogeneous HPC systems that include CPUs and GPUs. The aim is to assign resources based on specific job requirements, balancing individual job needs with overall system efficiency.

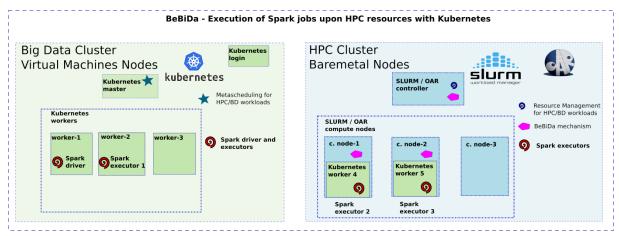

The next approach is *elastic resource management* with BeBiDa. This subsection explores BeBiDa, a system designed to enable elastic resource management for HPC systems,

particularly beneficial for Big Data workloads with dynamic resource requirements. The core concept of BeBiDa revolves around leveraging the prolog/epilog mechanisms of HPC resource managers. This allows for dynamic integration and removal of HPC nodes from a Kubernetes cluster. When an HPC job is submitted, the HPC node it occupies is detached from the Kubernetes cluster, effectively making it unavailable for Big Data jobs. Once the HPC job completes, the node is seamlessly re-integrated into the Kubernetes cluster, enabling Big Data jobs to utilize its resources once again. In this context, specific contributions provided new optimization techniques to guarantee the successful termination of Big Data jobs in a timely manner.

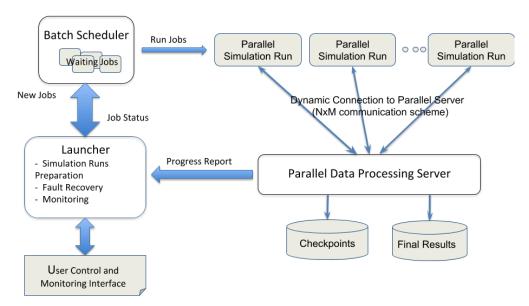

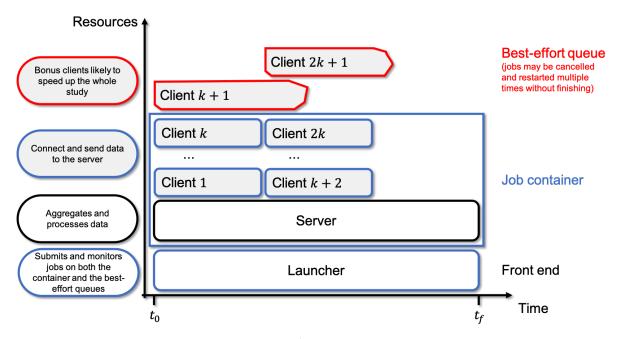

Finally, data-aware resource allocation has been investigated and implemented as a hybrid workflow scheduling. The approach for handling hybrid workflows utilizes traditional HPC job submission queues, alongside additional resources requested in a flexible "best-effort" queue. This allows an improved QoS for workflow by allocating dedicated resources, while using all idle resources whenever possible.

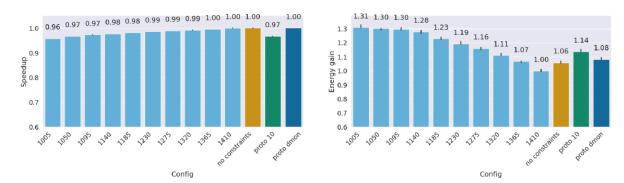

In section 3, energy savings are considered. More broadly this can be seen as an improvement in jobs per watt. First we look at *moldability for energy efficiency*: This research investigates moldability as a tool for improving energy efficiency in HPC systems. Moldability empowers resource managers to consider multiple configurations for a single job submission, enabling exploration of energy-efficient resource allocation options. An initial integration of energy-aware moldability policies in a resource management system is proposed. This integration utilizes a score function to evaluate configurations and select the one with the most favorable energy efficiency.

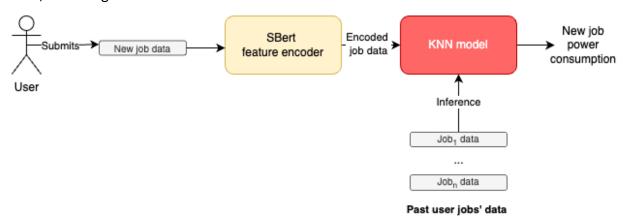

A novel approach for real-time power management in HPC data centers is then presented. This approach leverages machine learning models to predict job power consumption, eliminating the need for complex job power characterization. The proposed technique utilizes user data such as username, job name, and requested hardware specifications to predict power consumption.

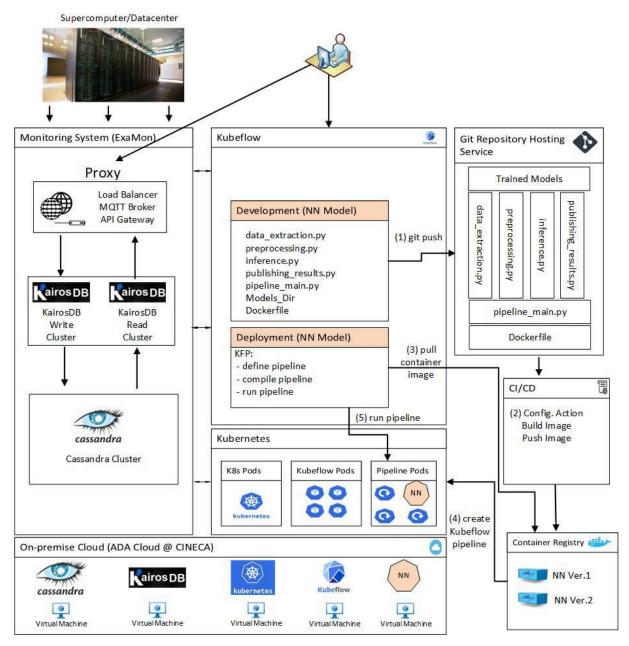

The report then details the integration of machine learning models into a comprehensive production system for HPC data centers. This system incorporates a multi-part framework with a monitoring subsystem that gathers sensor data to fuel the ML operation subsystem. Here, Docker containers and Kubernetes orchestrate the automated deployment, training, and utilization of the ML models. The trained models predict power consumption, enabling real-time optimization and resource management.

At the node level, optimizing GPU energy efficiency with BDPO integration is studied, exploring the integration of a runtime power management tool, BDPO, with GPUs for improved energy efficiency during HPC application execution. Similarly for CPUs, the utilization of on-chip controllers for thermal and power management within the REGALE prototype is detailed.

Section 4 investigates two techniques for managing power consumption in High-Performance Computing (HPC) systems under power constraints (often called power capping) while minimizing performance impact.

The first approach tackles power-capped situations by complementing the traditional First-Come-First-Served (FCFS) scheduling. It empowers users to designate jobs as EcoJobs, indicating their tolerance for running slower under power limitations. When power limitations are imposed, the resource manager prioritizes slowing down EcoJobs using Dynamic Voltage and Frequency Scaling (DVFS) techniques. This will reduce the power consumption of jobs under power caps, significantly reducing the number of jobs killed due to power limitations.

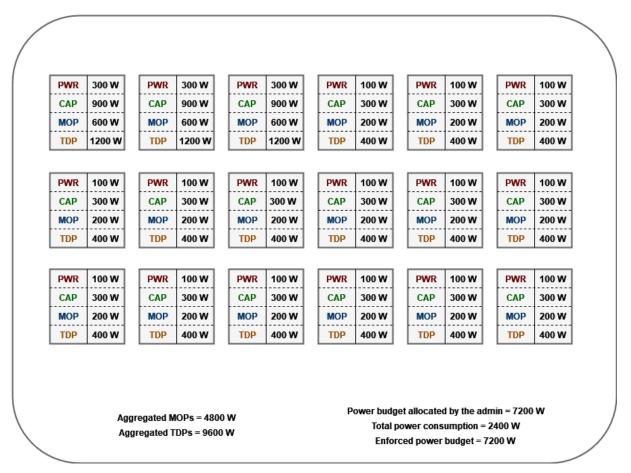

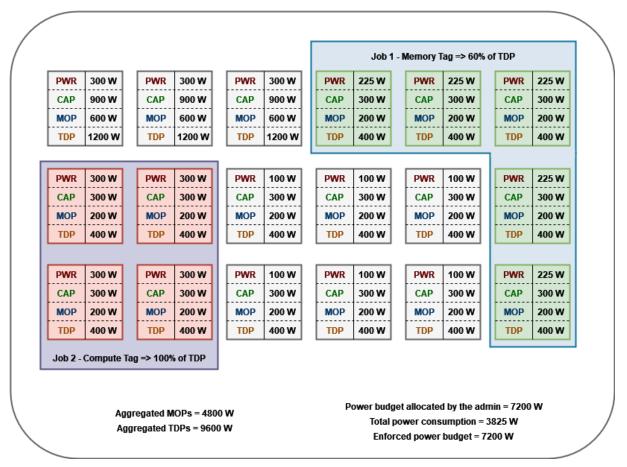

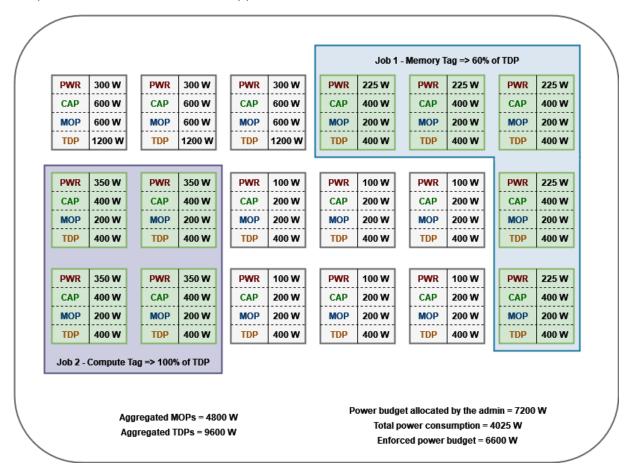

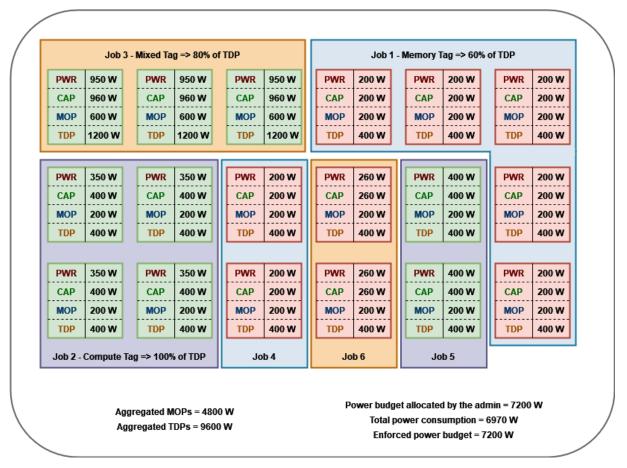

The second technique, Application-Aware Power Capping (AAPC), automatically addresses performance degradation caused by traditional power capping, which can significantly slow down compute-bound tasks. AAPC dynamically adjusts power budgets based on measured application characteristics like compute or memory intensiveness. By prioritizing compute-bound jobs (more susceptible to slowdowns) with efficient power allocations, AAPC aims to improve overall job throughput. The system integrates seamlessly with existing HPC software to leverage job information and manage power capping on individual compute nodes.

The power budget allocation algorithm prioritizes full power for memory-bound jobs, followed by mixed jobs. Compute-bound jobs have their power reduced only as a last resort. The study also addresses challenges associated with enforcing power caps due to delays between setting a cap and its actual application on compute nodes. To mitigate these delays, AAPC prioritizes stricter caps first and ensures enforcement only after reducing core frequencies.

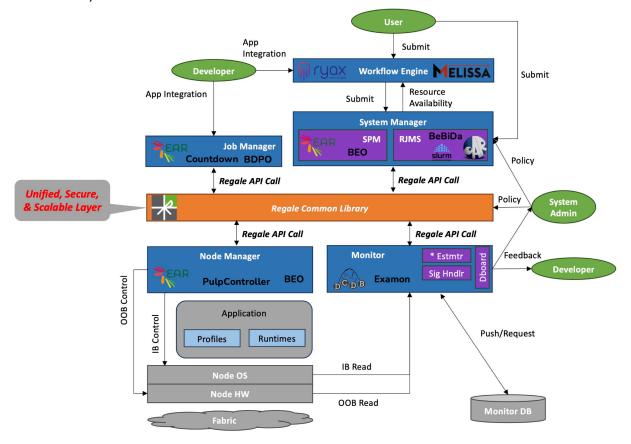

Finally, in Section 5 we explore the relations between all the proposed sophistications and their position in the REGALE Architecture detailed in Deliverable 1.3.

While the presentation focuses on the measurable improvements, a strong commitment to applicability and ease of use as defined in strategic objectives 2 and 3 was always present during the project. As a result most of the processes detailed in this report are fully transparent to the users.

**Note to the reviewers:** As this report is reporting on work spanning the whole project duration, some parts were already complete for the intermediate report D2.2. Specifically, Subsection 2.4 is almost identical to Subsection 2.4 in D2.2, and Subsection 3.4 has a few common pages with Subsection 2.3.B in the same D2.2 report. Quantitative and qualitative evaluations of the sophistications are presented in Deliverable 1.4.

# 2 Performance and Throughput

# 2.1 Co-scheduling for throughput and application coupling at the node level

## Motivation and problem definition

As we move towards exascale computing, the demands on process management in terms of flexibility and efficiency increase. Running multiple applications concurrently on a single node presents a potential solution to enhance resource utilization<sup>1,2</sup>. Moreover, today's processor manufacturers boost performance by increasing the number of cores within each CPU. However, not all high-performance computing (HPC) applications can fully leverage all cores on a single node, even when they scale across thousands of nodes. In such cases, resource sharing between applications on nodes can effectively distribute the load across various resources, improving overall utilization<sup>3</sup>.

The typical and most straightforward approach to resource management in modern supercomputing systems is to allocate full compute nodes to the applications. This means that a job requesting x processes from a system with y cores per node will receive [x/y]nodes to execute. While this scheme effectively ensures that tasks from diverse users do not negatively impact each other's performance, and additionally it is easy to implement, it comes at a substantial expense to system throughput and energy efficiency<sup>4</sup>. This is notably evident in the process of allocating a memory-bound application, which may face significant scalability problems. Quite importantly, several HPC applications are reported to have low operational intensity and thus are bound by the limited access to main memory. This family of applications would benefit from a resource allocation scheme that would provide more memory bandwidth, thus more memory links, i.e. in the concepts of resource management being spread in more nodes. Another study<sup>5</sup> emphasizes the redistribution of memory-bound applications across multiple nodes to alleviate performance bottlenecks and the co-location of jobs in a manner compatible with available resources, while another study<sup>6</sup> evaluates the co-allocation policy scheme in a simulated environment, indicating that co-scheduling has the potential to be a more efficient way to schedule jobs on high-end machines in both turnaround time and system and component utilization. On the other hand<sup>7</sup>, applications that spend a significant part of their execution time in communication may be sensitive to

<sup>&</sup>lt;sup>1</sup> Trinitis, C., and J. Weidendorfer. "Allocation-Internal Co-Scheduling." Co-Scheduling of HPC Applications 28 (2017): 46.

<sup>&</sup>lt;sup>2</sup> Brinkmann, André. "Co-scheduling: prospects and challenges." Co-Scheduling of HPC Applications 28.1 (2017): 20.

<sup>&</sup>lt;sup>3</sup> Frank, Alvaro, Tim Süß, and André Brinkmann. "Effects and benefits of node sharing strategies in hpc batch systems." 2019 IEEE International Parallel and Distributed Processing Symposium (IPDPS). IEEE, 2019.

<sup>&</sup>lt;sup>4</sup> Breslow, Alex D., et al. "The case for colocation of high performance computing workloads." Concurrency and Computation: Practice and Experience 28.2 (2016): 232-251.

<sup>&</sup>lt;sup>5</sup> Tang, Xiongchao, et al. "Spread-n-share: improving application performance and cluster throughput with resource-aware job placement." Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis. 2019.

<sup>&</sup>lt;sup>6</sup> Hall, Jason, et al. "Evaluating the Potential of Coscheduling on High-Performance Computing Systems." Workshop on Job Scheduling Strategies for Parallel Processing. Cham: Springer Nature Switzerland, 2023.

<sup>&</sup>lt;sup>7</sup> Bhatele, Abhinav, et al. "There goes the neighborhood: performance degradation due to nearby jobs." Proceedings of the International Conference on High Performance Computing, Networking, Storage and Analysis. 2013.

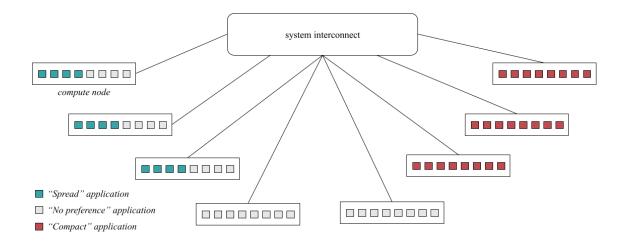

the number of nodes that they are allocated to, probably preferring to be mapped on a minimum number of nodes (although this may depend on the communication pattern and the underlying network setup). Finally, there exist applications that present no significant variation in their execution time due to different allocations in nodes. Figure 1 illustrates the recommended resource allocation strategy for the three application categories, specifically those that favor "spread", "compact", or "no preference".

**Figure 1:** Application categories based on resource allocation policy. In the "compact" category the application's processes are ideally packed together. In the "Spread" category the application's processes are assigned to half of the available cores in each CPU socket. In the "No preference" category the application's processes are assigned in a best-effort concept across all available cores.

#### Assumptions for a solution

The proposed approach revolves around a multi-step process aimed at optimizing resource allocation policies' assignments for high-performance computing (HPC) systems. The solution assumes that the allocation preference of the application is known to the system. This can be achieved in two ways, either the user explicitly requests for an explicit scheme, or the system is able to collect information from prior, historical runs of the application, and is able to associate previous runs with the forthcoming one. For this second case, the strategy entails the collection of performance counters from actual HPC benchmarks (targeted to implementations under the MPI standard) operating within real-world HPC systems. These performance counters serve as crucial data inputs for the subsequent step, which involves training a predictive model. This model leverages the collected performance counter data to make informed predictions about the most suitable allocation policy for new, incoming applications with known performance counters. In cases where no pre-existing data is available for a specific application, a generic allocation scheme is applied.

## Determination of the preferred resource allocation policy

Resource allocation policies ensure that computational resources are assigned optimally, maximizing the performance of HPC systems while minimizing operational expenses. By fine-tuning the allocation of resources, HPC facilities can reduce both power consumption

and the associated cooling costs. This not only makes HPC operations more cost-effective but also aligns with the broader goals of sustainability in the face of escalating energy demands. Table 1 serves as an informative reference, offering comprehensive descriptions of the various resource allocation policies, thus providing a detailed understanding of how resource distribution is managed.

**Table 1**: Resource allocation policies definition.

| No Preference | The allocation strategy is designed to first fill non-empty nodes, prioritizing those with the fewest available cores, and it only resorts to occupying empty nodes when no other options are available. This approach may lead to a combination of both occupied and unoccupied nodes, ensuring hardware-independent compatibility across heterogeneous clusters. This policy applies to jobs with no significant performance dropoff (e.g. compute-intensive applications).                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Compact       | This policy ideally packs processes together and fills up the minimum required number of nodes, creating the least possible node fragmentation. This intends to improve the performance of applications that invoke a large number of message exchanges. The allocation policy places emphasis on occupying initially vacant nodes, with a primary focus on nodes that reduce fragmentation by offering the maximum available cores. Only after considering empty nodes does it proceed to allocate resources to non-empty nodes with the priority to those that further minimize fragmentation. This strategy can result in a combination of both occupied and unoccupied nodes, making it versatile for use across hardware-independent, heterogeneous clusters. It stands in contrast to the "No Preference" allocation policy by explicitly favoring nodes that reduce fragmentation.                                        |

| Spread        | This policy allocates only half of the available cores in each CPU. The subsequent larger number of used nodes (i.e. memory links) provides a higher memory bandwidth for the application. This sparse allocation scheme is suitable for applications with higher memory demands. This variant of the allocation policy mirrors the "compact" approach but incorporates a new constraint -each step accounts for only half of a CPU socket. In cases where the requested cores are fewer than half the cores available in a CPU socket, the policy avoids spreading them across multiple sockets. Note that as the number of cores in a typical HPC node rises, we expect that this policy can be further enhanced to assume other allocation portions (most probably, quarters, eights, etc). For the sake of simplicity, in our current solution we work with half CPU allocation and leave the other options for future work. |

#### Performance counters and MPI time collection

Performance Counters (PCs) are a set of hardware-based or software-based metrics and counters that provide detailed information about the performance and behavior of a computer system, particularly during the execution of applications and workloads. These counters monitor various aspects of system performance, including CPU utilization, memory usage, I/O operations, cache hits, network traffic, and more. PCs are crucial tools for understanding and optimizing the performance of HPC applications and systems. Additionally, attributes allocated to MPI (Message Passing Interface) operations -which are essential for communication and coordination between parallel processes within the application's environment- can indicate a great impact on the overall performance of parallel applications. Due to their significant importance both metrics from PC and MPI Attributes are collected. The harvesting is systematically performed through the use of "perf" (a well-known and powerful performance analysis and profiling tool in Linux systems) and "mpiP" (a profiling tool designed for the MPI standard) utilities during runs under the "compact" resource allocation policy (default policy). The resulting data is conveniently organized and stored in CSV format file. The entire data collection and storage process is automated, sparing users from the intricacies involved. Users can effortlessly leverage these automated scripts by including the required file in their submission batch script, seamlessly integrating data collection into their workflow. These collected metrics serve as vital inputs for machine learning models, enabling data-driven insights and optimization in performance analysis. The metrics that are currently collected and used in the ML model training are the following:

- avg\_total\_time: Represents the average total time of the execution of a given application.

- compute time: Signifies the time spent on computational tasks.

- mpi\_time: Indicates the time allocated to MPI (Message Passing Interface) operations.

- ipc: Refers to the instructions per cycle, a measure of CPU efficiency.

- dp\_flops\_per\_node: Represents the double-precision floating-point operations per second per node.

- bw\_per\_node: Denotes the bandwidth per node, typically a measure of data transfer rate.

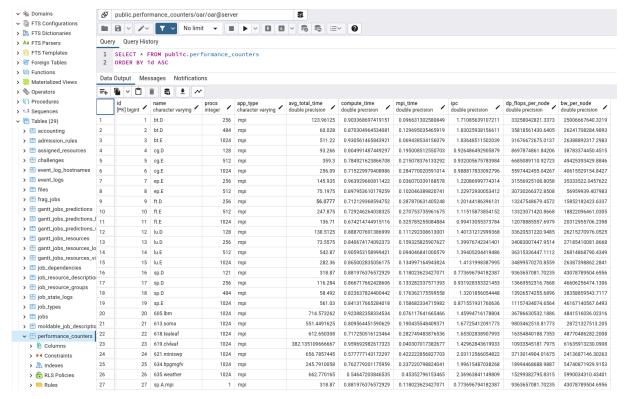

In our OAR3 implementation, the PostgreSQL table -shown in Figure 2- includes a column named "type" that signifies the specific parallel standard used during application execution and the corresponding metrics gathered. This functionality is designed for future flexibility, allowing the referencing of metrics for alternative parallel standards, such as OpenMP or hybrid OpenMP-MPI configurations. In this example, the type of applications in the table is "mpi".

**Figure 2:** A view of the PostgreSQL table integrated within the OAR3 database, depicting the collected Performance Counters and MPI time metrics. Data is produced by benchmarks' runs in actual HPC clusters. The implementation has a placeholder code to ingest new data to the table.

# Speedup heatmap generation

Co-scheduling, as a technique, entails the placement of pairs of processes from different jobs on common CPU sockets, aiming to enhance system throughput and subsequently greater energy efficiency. Colocating pairs of different jobs on a shared set of nodes within a supercomputer environment was used to generate a Speedup heatmap. A heatmap is a data visualization technique that represents data values as colors in a two-dimensional matrix. Our experiments involve running applications both solo ("compact") and in pairs ("co-scheduled") repeatedly for 10 minutes to generate multiple run logs. Speedup is then calculated as the ratio of the execution time of the "compact" to the execution time of the application in a co-scheduled state. Co-scheduling is performed by applying the "spread" resource allocation scheme for both applications and concurrently co-located them under the same compute nodes subset. For instance, assuming two applications A and B of x MPI processes each. The applications will be submitted on the same compute nodes with the allocation scheme of the "spread" policy where half of the CPU sockets will be filled by each application. This will lead to a full CPU socket capacity allocation, by heterogeneous MPI processes. Concerning the Speedup AR it would be the ratio of the execution time TA of application A in a "compact" allocation policy to the execution time of application A co-scheduled with application B TAB. A speedupAB of 2 means that application A runs two times faster if it is co-allocated with application B instead of running under the "compact" resource allocation policy.

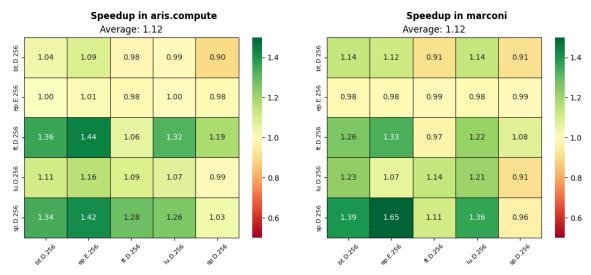

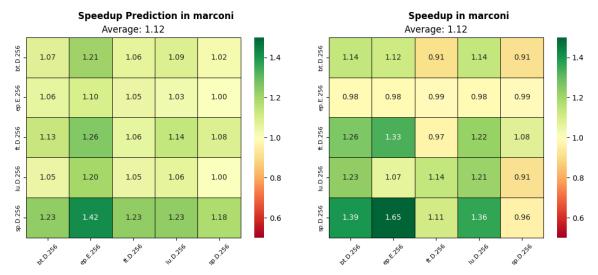

Speedup heatmaps are continuously populated with data collected from the ARIS supercomputer at GRNET<sup>8</sup>, and the MARCONI supercomputer at CINECA<sup>9</sup>, as depicted in Figure 3. It illustrates speedup heatmaps corresponding to individual supercomputers, showcasing results for identical pairs of the NAS Parallel Benchmarks<sup>10</sup>. The practical observation suggests that co-scheduling confers advantages to the HPC system, leading to a noteworthy 12% improvement in overall speed for both real-world HPC infrastructures, as opposed to the default allocation policy ("compact"). This performance gain is quite similar between these two HPC infrastructures, and it holds true despite variations in the characteristics of the compute nodes and the interconnections between the nodes of the clusters.

**Figure 3:** A view of the Speedup Heatmap per supercomputer for the same benchmarks co-schedulings. The application name underlines the problem that it is solved (e.g. sp), the size of the problem (e.g. D) and the number of MPI processes spawned (e.g. 256). As a significantly performance-gained example the co-scheduling of sp.D.256 and ep.E.256 leads to an average of 54% faster execution of the sp.D.256 benchmark in both HPC infrastructures, without reducing the execution time of the ep.E.256 benchmark as it was run under the "compact" policy.

## **Machine Learning model creation**

A Machine Learning (ML) model is a computational system that has undergone a training process to learn patterns and relationships within data. During training, the model is exposed to a dataset containing input data and their corresponding outcomes, and it adjusts its internal parameters and algorithms to make accurate predictions or classifications. In our work, in order to build the ML model, a small dataset of performance counters and MPI attributes harvested from runs of the NAS Parallel Benchmarks and the SPEChpc 2021<sup>11</sup> applications under the "compact" allocation policy on the ARIS supercomputer, was used. Each row is a fusion of two application's 6-feature set (avg\_total\_time, compute\_time, mpi time, ipc, dp flops per node, bw per node), forming a "Feature Vector", and includes

<sup>8</sup> https://hpc.grnet.gr

<sup>9</sup> https://www.hpc.cineca.it

<sup>10</sup> https://www.nas.nasa.gov/software/npb.html

<sup>11</sup> https://www.spec.org/hpc2021

the corresponding co-scheduling speedup derived from the Speedup Heatmap, as shown in Figure 4.

| Feature Vector  |          |     |                      |                |                       | y        |     |                      |                |         |

|-----------------|----------|-----|----------------------|----------------|-----------------------|----------|-----|----------------------|----------------|---------|

| Load A Load B   |          |     |                      |                | JOHNSON FOR SON, INC. |          |     |                      |                |         |

| Compute<br>Time | MPI Time | IPC | DP FLOPS<br>per node | BW per<br>node | Compute<br>Time       | MPI Time | IPC | DP FLOPS<br>per node | BW per<br>node | Speedup |

**Figure 4:** A representation of a row of the dataset that is used to train the ML model. The "Feature Vector" was derived from runs under the "compact" allocation strategy, whereas the "y" is the speedup derived from a co-schedule run between the respective applications.

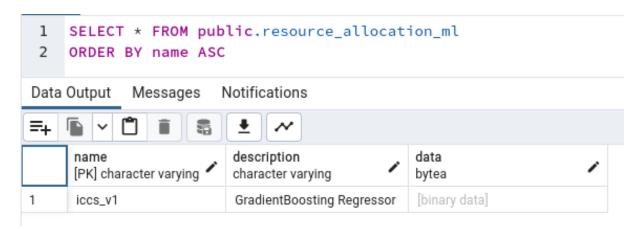

A variety of linear, non-linear, and ensemble learning regression models from scikit-learn Python library were trained on the dataset. The data was split into 70% for training and 30% for testing. During the training phase, grid search was employed to optimize the model's hyperparameters, combined with a 5-fold cross-validation process. In the testing phase, the performance of these models was assessed and compared using metrics such as RMS and absolute error to evaluate their predictive accuracy. Our OAR3 implementation facilitates the ingestion of diverse models into the database, offering flexibility in choosing how to utilize them, as it is shown in Figure 5. Utilizing various ML models for predictions leverages their individual strengths, leading to improved accuracy and robustness in predictive tasks. It also allows for better adaptation to diverse data and problem scenarios.

**Figure 5:** A view of the Machine Learning model as it is stored in the OAR3 PostgreSQL database. The implementation is able to store and load for use multi-purpose models.

A captivating aspect of the ML model's predictions can be seen in the scenario illustrated in Figure 6. In the leftmost figure, you can observe a prediction generated by the ML model using performance counters and MPI time data ("Feature Vector") collected from the NAS Parallel Benchmarks executed under the "compact" allocation policy on the Marconi supercomputer. The figure on the right displays the real speedup heatmap achieved by co-scheduling these specific NAS Parallel benchmark cases, as previously presented in Figure 5. As previously indicated, the ML model has been trained using data from runs of the NAS Parallel Benchmarks and the SPEChpc 2021 applications conducted under the "compact" allocation policy on the ARIS supercomputer. Another intriguing aspect is that the ML model

accurately predicted the same average Speedup, despite having no other information beyond the "Feature Vector" of the potential co-schedule.

**Figure 6:** A view of the predicted Speedup Heatmap vs the actual Speedup Heatmap in Marconi. The prediction is performed by the ML model based on the "Feature Vector" gathered from the NAS Parallel benchmarks on Marconi, under the "compact" policy.

#### **Integration within OAR3**

A Resource and Job Management System (RJMS) is a software stack used in high-performance computing (HPC) to manage and coordinate the allocation of computational resources and the scheduling of jobs submitted by users. A typical workflow in RJMS consists of six core steps. Initially, it begins with job submission, where users provide job details and request to run a job in the cluster. Following, jobs are then queued based on various factors such as priority and fairness, and then resource allocation follows assigning resources to jobs. Afterward, the job is executed, which involves running the task while monitoring progress. Eventually, when the job is completed, the system updates the status and provides the respective results. Finally, in the job cleanup step, the system manages post-job tasks and resource releases.

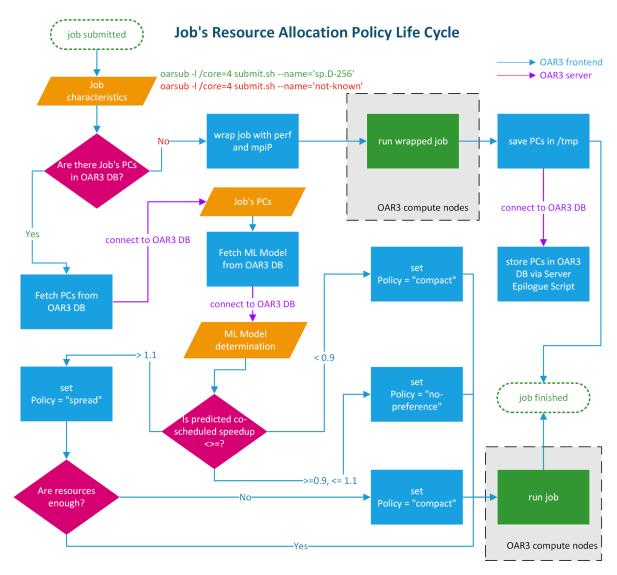

**Figure 7:** Life Cycle of job's resource allocation policy assignment in OAR3 integration. The Admission Rule reads the ML model with the corresponding Performance Counters and MPI time of the application and automatically assigns the policy (i.e. compact, spread, no\_preference) based on its prediction design.

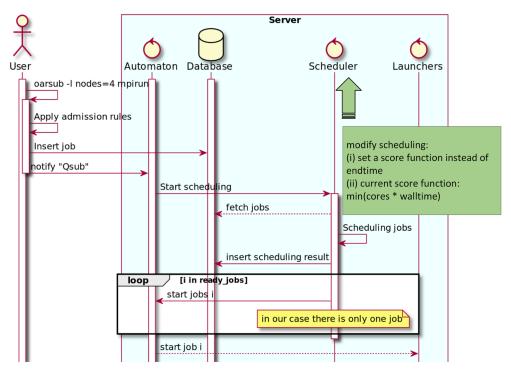

Our work integration within OAR3 is covered in Figure 7, where the process flow of the co-scheduling functionality is visually represented and subsequently subjected to a step-by-step analysis. In the initial phase, a job is submitted by the user with the "oarsub" command. Afterward, an Admission Rule (AR) -an OAR3 mechanism to perform tasks between the user's input and the job's submission- analyzes the job's characteristics and inquires about the availability of Performance Counters (PCs) specific to the given job. In order to fulfil this task, the system establishes a connection with the OAR3 database to ascertain the presence of these counters. If they are available, the system retrieves both the PCs and a Machine Learning (ML) model from the OAR3 database. The PCs are then provided to the ML model, which, based on its predictions, determines the allocation policy for the job. This policy is set automatically by the AR as one of the following options: "compact", "spread", or "no-preference". In the case of the "spread" policy where double the resources

are required, verification is conducted to ascertain whether the cluster possesses the capacity to accommodate this allocation. If the cluster lacks the necessary capacity, the allocation policy is converted to "compact" and the subsequent steps adhere to the standard workflow. In instances where PCs cannot be located for the job, the "perf" and the "mpiP" utilities are employed to encapsulate the job command and capture the relevant performance metrics. Following this, the job is submitted, and when it is executed, an epilogue script is executed on the server. This script collects the captured metrics and stores them within the PCs' table in the OAR3 database for that particular job name. Throughout the entire process, all procedural steps are executed within the OAR3 frontend node. The interactions with the OAR3 database are facilitated through the server node. In contrast, the computational aspects are unequivocally executed on the compute nodes.

Within Table 2, we have encapsulated our contributions, showcasing the corresponding source code alongside comprehensive information pertaining to the associated branches and releases.

| Name                                  | Description                                                                                                  | Repository                                             | Branc<br>h | Release/<br>Tag | Based on oar-team |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------|-----------------|-------------------|

| Co-scheduling<br>at the node<br>level | Implementation of new resource allocation policies with auto-assignment using trained ML model               | https://github.com/cslab-ntua<br>/oar3                 | master     | 3.0.0.dev1<br>0 | 2023/10           |

| Ecosystem of OAR3                     | All the necessary<br>dependencies,<br>libraries, and OAR3<br>setup's<br>characteristics and<br>configuration | https://github.com/cslab-ntua<br>/regale-nixos-compose | main       | 1.1             | 2023/10           |

**Table 2**: Software implementation repositories.

#### 2.2 Co-scheduling within multicore processing units

#### Motivation

HPC clusters and supercomputers are becoming increasingly heterogeneous, consisting of CPUs and GPUs. In fact, around 190 of top-class supercomputers ranked in the Top500 list are GPU-equipped systems as of Nov 2023. Although exploiting GPU resources is indispensable on such systems, which is because they offer a large fraction of computational throughput and memory bandwidth, it is becoming more and more difficult to fully utilise the entire resources within a GPU chip by one single program. The first reason for this is not all GPU programs have sufficient parallelism to convert the available compute resources inside a GPU into speedup, which is governed by the well-known Amdahl's law. The second

reason is the throughput of memory intensive applications is limited by the available memory bandwidth, and thus increasing the compute resources does not contribute to the speedup for them, which is known as the memory-wall problem. The third reason is the compute resources inside a GPU are also becoming heterogeneous with different types of units (e.g., matrix engines, regular FP64 units, integer units, etc.), and depending on their usages, power can also be underutilised and wasted.

#### **Problem Definition**

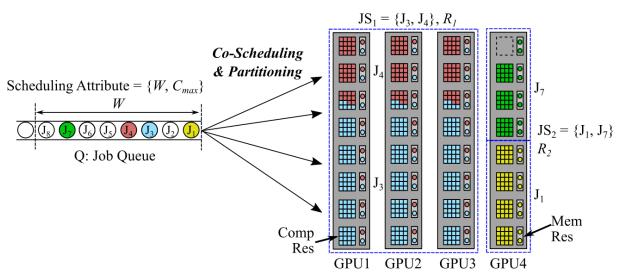

Figure 8 illustrates our GPU co-scheduling and resource partitioning problem. We target W GPU jobs waiting within the window (size: W) on a given queue and attempt to minimise the total execution time of W different GPU jobs. Instead of executing them one by one, we consider dividing them into several sets of jobs and co-locate each set on the same GPU(s) in a space sharing manner while optimising the resource allocations to the co-located jobs. Here, we assume the concurrency of co-scheduling (or the number of co-located jobs) on each GPU is less than or equal to a given threshold (C<sub>max</sub>) and the requested numbers of nodes/GPUs are the same for all jobs in a set, namely the same sized GPU jobs can be co-scheduled. For each set of co-scheduling jobs, we optimise the resource partitioning state on the allocated GPU(s), and to this end, we utilise several GPU partitioning features that recent commercial high-end GPUs support (e.g. NVIDIA MIG, NVIDIA MPS, etc.). With the MPS feature, one can partition/assign compute resources to co-located jobs at arbitrary rates in a fine-grained manner, while with the MIG feature, one can completely isolate multiple co-located jobs, resulting in coarse-grained but interference-free co-scheduling.

Figure 8: GPU co-scheduling and resource partitioning problem

#### Assumptions for a solution

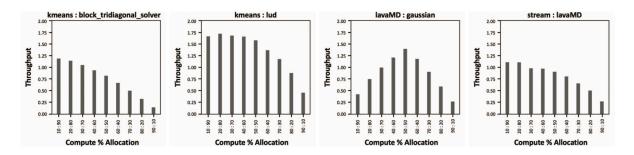

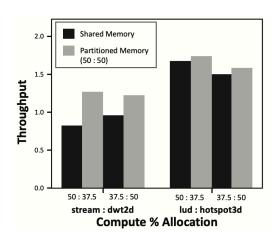

Figure 9 demonstrates GPU throughput as a function of compute resource allocation to two co-located HPC benchmark programs across different program mixes. For this evaluation we

used our testbed system equipped with an NVIDIA A100 GPU with the MPS feature enabled. The X-axis represents the ratios of compute resource allocation to the co-scheduled programs shown at the legend, while the Y-axis indicates the relative throughput normalised to that of a time-sharing scheduling, i.e., executing these two programs one by one without sharing the resources but with fully allocating the entire GPU resources. As illustrated in the figure, the optimal allocation of compute resources to the co-located programs depends highly on the given programs and their characteristics (e.g. compute/memory intensity). As we can observe in the third case, a balanced allocation achieves the best performance, while for the others, a skewed allocation has advantage over a balanced one with a unique optimal allocation point.

Figure 9: Co-scheduling Throughput as a Function of Compute Resource Allocations using MPS Partitioning

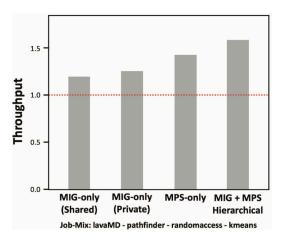

The left graph in Figure 10 presents the impact of memory bandwidth resource partitioning while using two different options (shared or private) offered by the NVIDIA MIG feature. The X-axis lists two different job mixes with two different compute resource allocation rates as well as two different memory options (shared or partitioned), while the Y-axis shows the relative throughput normalised to that of the time-sharing scheduling as mentioned above. To assess the impact of memory partitioning on performance, we set up exactly the same compute resource allocation for the shared and partitioned options. For these job mixes, we observe considerable speedup by partitioning/isolating memory bandwidth resources by mitigating the interference impact among the co-located programs. Therefore, depending on the given job mix, it is preferable to partition/isolate the shared memory resources in order to mitigate the interference impact. Finally, the right graph in Figure 10 compares multiple different partitioning options. The vertical axis indicates the relative throughput normalised to that of the time-sharing scheduling mentioned above. For this job mix, the MIG+MPS hierarchical option works the best.

**Figure 10:** Performance Benefit of Bandwidth Partitioning (Left) and Performance Comparison for Different Partitioning Variants (Right)

Judging from the observations above, it is very important to choose the right combinations of jobs to co-schedule. At the same time, it is essential to have sufficient variants of resource partitioning and select the optimal one from them for a given set of co-scheduling jobs.

#### **Solution Overview**

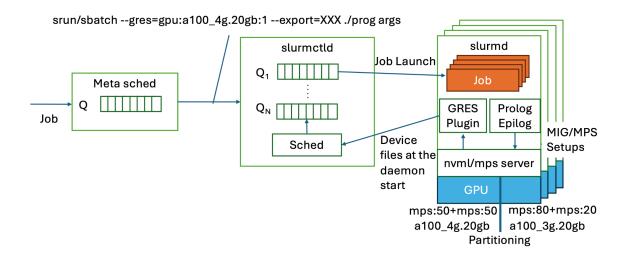

Our approach requires (1) hardware support for enabling GPU partitioning; (2) software interface to interact with the hardware partitioning configuration; (3) RJMS support for job resource-wise scheduling; and (4) capability of RJMS node daemon to read/control the GPU partitioning via an associated software interface. So far the following selections meet the above requirements: NVIDIA Multi-Process Service (MPS) or NVIDIA Multi-Instance GPU (MIG); NVIDIA Management Library (NVML); and Generic Resource (GRES) plugin in the SLURM scheduler (partly supported). The default GRES plugin has several limitations to control the GPU partitioning. For MIG, it can recognize the device files of MIG partitions at the slurmd launch, however it does not control the MIG device setup nor reloads newly added device files generated by creating new MIG partitions. For MPS, the default MPS plugin does not offer per GPU / MIG partition MPS setting. Alternatively, we control MIG/MPS settings via our prolog script to offer a functionality to control MIG/MPS hierarchical partitioning as per request.

Figure 11 illustrates an overview of our approach that works over the GPU partitioning functionality offered by the above software/hardware mechanisms. Our approach optimises co-scheduling GPU job pair selections along with GPU partitioning configurations (MPS/MIG).

Figure 11: Overall Architecture

#### An ML-based Sophistication in the Meta Scheduler

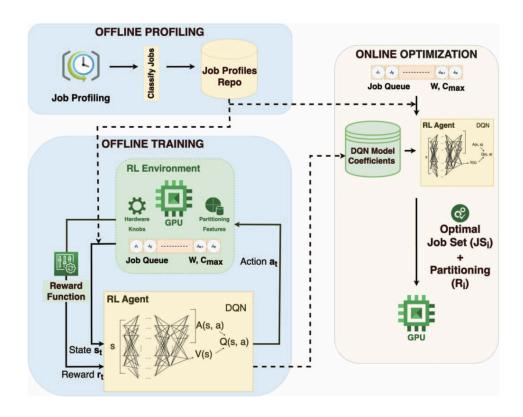

Figure 12 illustrates the entire system architecture of our solution. As shown in the figure, the overall solution consists of three parts: (1) the offline profiling to collect application profiles; (2) the offline training to set up the coefficients of our agent; and (3) the online optimization to apply the trained agent to the decision making.

Figure 12: System Architecture of the Meta Scheduler

For the application profiling, we collect hardware performance counters to characterise the running jobs on the target system. The profiles need to be collected beforehand for any co-scheduling targets in both the offline and online phases. In the offline training phase, we collect the solo-run profiles for all the benchmark programs before the model training. In the online optimization phase, if no profile is available for a queuing job, it is excluded from the co-scheduling target and is executed exclusively using the entire GPU while collecting the profile that shall be stored in the Job Profiles Repository. If the application is executed again on the system, it is included in the co-scheduling target as the profile is available in the repository. This procedure requires a matching function to select a corresponding profile for each job based on its submission information (e.g., binary path, user ID, etc.). In the current version, we simply consider using the application binary path plus name as a key and checking if there is a profile associated with it in the repository. Note, developing an advanced way to generate the key from the job submission information, while taking a variety of aspects into account (e.g., input dependency), is an open problem for profile-based approaches.

For the offline model training, we create variants of benchmark program mixes to co-locate on the target GPU. For each program mix, we continuously examine the co-run throughput while changing the partitioning setup. This partitioning search is based on reinforcement learning, i.e., we update the partitioning and resource allocations accordingly when the next co-run (with the exact same program mix) based on the reward function output that takes the co-run throughput into account. During this procedure, the state-action table, which is approximated by a neural network in this study, is trained, and the model coefficients in the agent are eventually determined. The model coefficients are hardware specific and are not portable to different hardware, however the training procedure is required only once for a system though.

In the online phase, we deploy an optimization agent using the model generated in the offline phase. The agent regards the optimization as a classification problem and uses the model to choose sets of co-scheduling job mixes and corresponding resource allocations to maximise the GPU throughput.

#### 2.3 Elastic Resource Management

#### **Motivation and Background**

HPC systems are by design rigid in the way resource management takes place. This is because in contrast with Cloud systems the HPC system managers consider executions with time constraints which enables them to have optimal control of how the computing resources are used, achieve higher system utilization, manage to serve higher demand of requests, provide higher scalability and minimize system fragmentation. In more detail the HPC system managers provide the ways to perform allocations of resources specifying both space and time requirements. They allow users to demand particular computing resources (such as

number of nodes, cores, amount of RAM per core, number of GPUs, etc) for a certain amount of time. If the time limit for the job is not added and by default a small time limit is given by the system.

Another aspect related to the rigidness of HPC is their inability to support evolving jobs, which are those jobs that may need a dynamic scale-out (grow) or scale-in (shrink) of their amount of allocated resources. The typical but inefficient practice to satisfy evolving jobs with the traditional HPC resource managers is to allocate in advance the complete amount of resources which will be used during the whole execution of the evolving job which may mean that certain resources will be allocated but not utilized.

Evolving jobs were not the typical example of HPC jobs but with the increasing needs of Big Data and AI workloads to leverage HPC instruments we want to bring more elasticity in HPC in order to enable the efficient execution of these types of jobs and allow them to leverage the computing capabilities of HPC.

The time-constrained, non-dynamic mode of scheduling which fits very well to the High Performance Computing characteristics of these systems is not adapted for Big Data jobs which are more elastic by nature. In typical Big Data frameworks such as Spark and Flink the jobs are launched as Cloud services without time limits and have the ability to scale-out/in rapidly whenever they need.

In this task we want to bring more elasticity in HPC but without altering its resource manager's internal aspects or losing in scheduling efficiency. We are convinced that each scheduling mode (HPC and Big Data) have their own advantages and disadvantages and they fit better to serve the needs of their typical use cases hence we do not want to change internals of any of them. For that, we study and extend techniques that enable the HPC and Big Data resource and job management systems to collocate with minimal interference on the HPC side but with acceptable and high guarantees for the Big Data jobs executions.

#### **Towards Elasticity in HPC for Big Data jobs**

HPC and Big Data resource and job management systems are complex pieces of software, and their interaction is not an easy task. In our case we are interested in the interoperability of Slurm and OAR HPC resource managers with Kubernetes as a Big Data resource manager. Big Data workloads that make use of ML frameworks such as PyTorch, Tensorflow or Horovod do not use a Big Data resource manager within their runtime and hence it is easier to allow an HPC resource manager to schedule these workloads and deploy them with singularity containers. However, in the case of Spark applications things are more complex. While the standalone mode can allow the simple static execution of jobs, which can easily be executed by Slurm and Singularity; In the cluster mode an external resource manager gives more intelligence and elasticity in the executions. In our case, Kubernetes can play the role of resource manager for Spark framework based on already existing developments<sup>12</sup> done by the community. However, these Spark workloads will need to collocate with other HPC

12.04.2024

REGALE - 956560 24

<sup>&</sup>lt;sup>12</sup> Spark - Kubernetes integration: <a href="https://spark.apache.org/docs/latest/running-on-kubernetes.html">https://spark.apache.org/docs/latest/running-on-kubernetes.html</a>

workloads on the HPC side, which is managed by another resource manager, Slurm or OAR. The simplest way is to give precedence to one workload over another. HPC jobs have tighter resource requirements, while the Big Data applications are designed to manage resource dynamicity. It is possible to combine the characteristics of each type of workload and achieve optimal behavior for both types of workloads by leveraging: the prolog/epilog mechanism that most of the HPC resource managers offer, along with the capacity of the Big Data resource manager to handle a dynamic number of nodes.

The work in this section makes use of the developments to support Kubernetes for Spark and combines it with previous works<sup>13</sup> upon collocation of Big Data and HPC jobs through the technique of prolog/epilog scripts. This software tool, named BeBiDa, is based on executing Spark applications upon unutilized resources by the HPC resource manager and whenever normal HPC jobs need the resources then Spark instances are removed, and they are restarted elsewhere when there is availability. In these previous works the developments and experiments have been done using Spark jobs with YARN resource manager on the Big Data side along with OAR resource manager on HPC side. In the context of REGALE, we have adapted the technique for Kubernetes on the Big Data side, Slurm and OAR on the HPC side and we have provided the support of the Singularity containerization platform in order to enable flexible environment deployment on HPC clusters.

Initially, in the context of REGALE, the BeBiDa technique has been enhanced for Kubernetes and Singularity, using only Singularity-CRI and Slurm resource manager. The initial version of the prototype implementation can be found here: <a href="https://github.com/RyaxTech/bigdata-hpc-collocation">https://github.com/RyaxTech/bigdata-hpc-collocation</a>

This final version of the prototype implementation has enabled the tight integration of Kubernetes along with the support of both SLURM and OAR resource managers. The code of final version of BeBiDa for Kubernetes, Slurm, OAR and Spark can be found here: <a href="https://github.com/oar-team/regale-nixos-compose/tree/main/bebida">https://github.com/oar-team/regale-nixos-compose/tree/main/bebida</a>

The integration of BeBiDa with Kubernetes goes a step further in enabling an elastic resource management for HPC systems, since it allows to bring Spark environment, or other Big Data related environments, on HPC systems.

In our setting we consider that there will be an HPC cluster managed by SLURM and a small Big Data cluster managed by Kubernetes. Big Data jobs launched on the Kubernetes side may have the ability to make use of the HPC cluster in best-effort mode. On the Big Data side we could just have 1 or 2 nodes with Kubernetes executors in order to host the Spark driver jobs. In case of total usage of resources on the HPC side the Big Data cluster resources could serve some minimum requirements for Spark jobs.

To better understand the resource sharing mechanism let us take a simple example of one HPC cluster shared between two applications: an MPI job and a Spark application. In this

<sup>&</sup>lt;sup>13</sup> Michael Mercier, David Glesser, Yiannis Georgiou, Olivier Richard. Big data and HPC collocation: Using HPC idle resources for Big Data analytics. BigData 2017: 347-352

configuration, the Spark application is submitted to the Big Data resource manager, this application can take advantage of all the available resources of the Big Data cluster and the unutilized resources on the HPC cluster. When an MPI application is submitted to the HPC cluster, the resources previously used by the Spark application are removed from it and allocated to the MPI one. The Spark built-in resilience mechanism will handle this resource loss and split the work between the remaining resources. When the HPC jobs finishes, the freed resources will be allocated again to the Kubernetes cluster and the Spark application might use them again.

The advantage of this solution is that it is simple to implement – only based on configuration and integration – but still gives the flexibility to have HPC resources available for data analytics applications. As a comparison, in a classical setup of two clusters (HPC and Big Data), it is possible for a Spark application to run in stand-alone mode inside an HPC job, but then it cannot leverage resources from both Big Data and HPC clusters. Whereas if it is scheduled through Kubernetes, it can make use of both clusters dynamically and both HPC and Big Data workloads can co-exist efficiently, leveraging both clusters without keeping resources unutilized while others may be fragmented. This technique can be used in the context of Spark for batch executions, but can be also used, with minor changes, in the context of Streaming such as Spark Streaming [3] or Flink.

The main drawback of the solution is that it needs the installation of Kubernetes Node components on the HPC nodes participating in the Kubernetes cluster to be leveraged for Big Data jobs executions. Besides the installation of some additional software the main issue is the security concerns brought by the container runtime interfaces used by Kubernetes. However, this is continuously being improved by the community and since the beginning of REGALE project we have now effective and secure ways to deploy Kubernetes node components as a non-root user<sup>14</sup> helping to remove the security concerns.

#### Configuration and automation of BeBiDa tool for elastic executions on HPC

We hereby show some basic configuration steps, provided to enable the features to take place. The resource sharing between the HPC and the BD clusters is implemented by attaching the idle resources of the HPC cluster to the Kubernetes cluster. This mechanism is implemented using the HPC resource manager prolog and epilog scripts. Each HPC worker node is a Kubernetes worker which is decommissioned if an HPC job requires the node and re-attached to the pool of Kubernetes workers when the job finishes.

The following terminal details show the contents of the OAR prolog and epilog scripts. Similar scripts are used in the case of SLURM. The prolog script features the drain of the Kubernetes node and its removal from Kubernetes cluster available resources in order to be used by OAR HPC jobs. We can also see the definition of "BEBIDA\_NOOP" job-name which, as we will see in the next section, is used for the optimization techniques.

#### #!/bin/bash

**REGALE - 956560** 26 12.04.2024

<sup>14</sup> https://kubernetes.io/docs/tasks/administer-cluster/kubelet-in-userns/

```

export OAR JOB ID=$1

export PATH=$PATH:/run/current-system/sw/bin:/run/wrappers/bin

echo Enter BEBIDA prolog

printenv

id

if [ "$OAR JOB NAME" = "BEBIDA NOOP" ]

then

echo BEBIDA_NOOP is set. Do not stop the kubernetes agent

exit 0

fi

for node in $(oarstat -J -j "$OAR_JOB_ID" -p | jq

".[\"$OAR JOB ID\"][] | .network address" -r)

do

echo == Removing node $node

oardodo kubectl --kubeconfig /etc/rancher/k3s/k3s.yaml drain

--force --grace-period=5 --ignore-daemonsets --delete-emptydir-data

--timeout=15s $node

echo == Removed node $node

done

) > /tmp/oar-${OAR_JOB_ID}-prolog-logs 2>

/tmp/oar-${OAR JOB ID}-prolog-logs

```

The epilog script features the uncordon of the Kubernetes node and its to the Kubernetes cluster available resources for Big Data jobs executions.

```

#!/bin/bash

export OAR_JOB_ID=$1

export PATH=$PATH:/run/current-system/sw/bin:/run/wrappers/bin

(

echo BEBIDA epilog

printenv

id

for node in $(oarstat -J -j "$OAR_JOB_ID" -p | jq

".[\"$OAR_JOB_ID\"][] | .network_address" -r)

```

```

do

echo == Adding node $node

oardodo kubectl --kubeconfig /etc/rancher/k3s/k3s.yaml uncordon

$node

echo == Added node $node

done

) > /tmp/oar-${OAR_JOB_ID}-epilog-logs 2>

/tmp/oar-${OAR_JOB_ID}-epilog-logs

```

Once these scripts are set in the OAR configuration of each HPC compute node to be added in the HPC-Big Data collocation pool of nodes, and the right changes are made in the OAR configuration files; the addition and removal of HPC nodes in the Kubernetes cluster will be done automatically.

Finally, Spark needs to be configured in order to have Kubernetes defined as its cluster manager. The main configuration change is the creation of a serviceAccount within Kubernetes which will grant kubernetes access required to Spark to spawn the workers across the desired Kubernetes nodes on the HPC side.

```

apiVersion: v1

kind: ServiceAccount

metadata:

name: spark

namespace: default

apiVersion: rbac.authorization.k8s.io/v1

kind: Role

metadata:

namespace: default

name: spark-role

rules:

- apiGroups: [""]

resources: ["configmaps"]

verbs: ["*"]

- apiGroups: [""]

resources: ["pods"]

verbs: ["*"]

- apiGroups: [""]

resources: ["services"]

verbs: ["*"]

```

apiVersion: rbac.authorization.k8s.io/v1

kind: RoleBinding

metadata:

name: spark-role-binding

namespace: default

subjects:

- kind: ServiceAccount

name: spark

namespace: ryaxns-execs

roleRef:

kind: Role

name: spark-role

apiGroup: rbac.authorization.k8s.io

By doing that we give the ability to Kubernetes to perform the scheduling decisions for Spark instead of Spark standalone scheduler, hence taking advantage of the power of Kubernetes scheduling algorithms.

#### **Experimenting the elastic execution of Big Data jobs upon HPC resources**

Once the environment is configured, we can launch a Spark job to be deployed on HPC clusters leveraging on the dynamic nature of Spark jobs without interfering with the rigid HPC executions.

We provide here a simple example of experimenting with the BeBiDa system management tool to enable the elastic execution of Spark jobs on HPC resources. Once the environment is ready we will see that Spark will launch the driver which will be deployed on the Kubernetes side and then depending on the availability of Kubernetes workers it will deploy the Spark executors. Figure 13 provides a high-level view of how this deployment will take place among the available resources of Big Data and HPC clusters. In the figure we can see an execution with 3 executors where 1 lies on the Big Data cluster while the other 2 executors lie on the HPC cluster.

Now once the Spark job is deployed and we can see how the HPC nodes are used for its execution, we can then deploy an HPC job on the HPC side selecting the compute node 1 and observe how the Spark executor 2 running on the HPC cluster will be killed since the Kubernetes worker 4 will be stopped there so that the HPC job which has higher priority can be executed without interference. Nevertheless, the Spark job will deploy the Spark executor 2 and resume execution (without needing to restart from the beginning) on other available nodes and in particular it will try to use the HPC compute node 3 if it is not used by an HPC job. This will allow both the higher priority rigid HPC Slurm job and the dynamic Spark one to be run successfully.

Figure 13: The high-level view of a Spark job execution on HPC resources elastically through BeBiDa

In our procedure, we have made use of NixOS-Compose tool<sup>15</sup> to provide a reproducible methodology to seamlessly prepare the environment on a PC, using VMs, and on Grid5000, using baremetal machines. The procedure is detailed here <a href="https://github.com/oar-team/regale-nixos-compose/tree/main/bebida">https://github.com/oar-team/regale-nixos-compose/tree/main/bebida</a> but we provide an example right beneath for a VM based experimentation.

We can either deploy BeBiDa environment with OAR or SLURM resource manager.

```

$cd regale-nixos-compose/bebida

# Build the environment with OAR

$nxc build -C oar::vm

# OR use the following for SLURM nxc build -C slurm::vm

export MEM=2048

nxc start

```

We can wait for the VM to start, and then in another terminal (in the same directory), you can connect to the frontend with:

```

$nxc connect frontend

```

We can check that OAR has two nodes alive with oarnodes:

```

[user@frontend:~]# oarnodes -s

node1:

1: Alive

node2:

2: Alive

```

<sup>15</sup> https://github.com/oar-team/nixos-compose

We can then connect to the server to check that Kubernetes is also seeing the nodes as Ready:

#### \$nxc connect server

```

[user@server:~]# kubectl get nodes

NAME

STATUS

ROLES

AGE

VERSION

control-plane, master

2m48s

v1.23.6+k3s1

server

Ready

v1.23.6+k3s1

node2

Ready

2m36s

<none>

2m36s

v1.23.6+k3s1

node1

Ready

<none>

```

Now we can use OAR and Kubernetes with Bebida enabled. On the server we can watch the Kubernetes nodes state with kubectl get nodes -w, where we can see:

```

[user@server:~]# kubectl get nodes -w

NAME

STATUS

ROLES

AGE

VERSION

7m35s

v1.23.6+k3s1

server

Ready

control-plane, master

7m23s

v1.23.6+k3s1

node2

Ready

<none>

v1.23.6+k3s1

node1

7m23s

Ready

<none>

```

Then we can deploy a simple Spark job execution based on the Spark-pi example here: <a href="https://github.com/oar-team/regale-nixos-compose/blob/main/bebida/scripts/spark-pi.yaml">https://github.com/oar-team/regale-nixos-compose/blob/main/bebida/scripts/spark-pi.yaml</a>

```

[user@server:~]# kubectl apply -f scripts/spark-pi.yaml

```

We can then observe how the Spark executors are deployed across the available Kubernetes resources on either the Big Data or the HPC cluster (through BeBiDa tool)

While this Spark job is running we can go on the frontend node and we can create a simple OAR job

```

[user@frontend:~]# oarsub -l nodes=1 hostname

# INFO: Moldable instance: 1 Estimated nb resources: 1

Walltime: 3600

```

# OAR\_JOB\_ID=2

We will then observe in the server terminal that the node allocated to the OAR job becomes unavailable for the Kubernetes workload (SchedulingDisabled), during the OAR job execution and then after some seconds it comes back in a Ready state:

| <pre>node1 Ready,SchedulingDisabled v1.23.6+k3s1</pre> | <none></none> | 8m11s |

|--------------------------------------------------------|---------------|-------|

| <pre>node1 Ready,SchedulingDisabled v1.23.6+k3s1</pre> | <none></none> | 8m11s |

| node1 Ready<br>v1.23.6+k3s1                            | <none></none> | 8m15s |

In the meantime we can obslerve that the Spark executor which was running on the particular node has been removed, since the node was no longer part of the Kubernetes nodes, and it has been placed upon a different available node.

An important aspect that needs to be improved is the execution guarantees we can give on the Big Data jobs when executed elastically on the HPC side through BeBiDa. The current problem is that since HPC jobs have priority and Big Data jobs are always launched on the unutilized resources of the HPC system, it is possible that we do not manage to finalize Big Data jobs in a timely manner. This means that we cannot easily use this technique for real-time Big Data streaming cases. Optimizations are needed to the BeBiDa technique in order to address this issue. This is the subject of the following section.

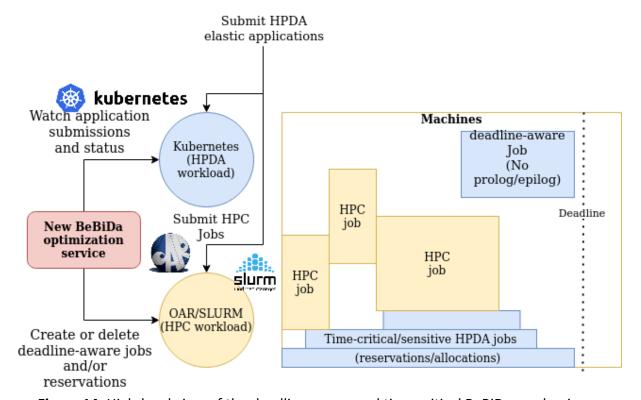

#### Improving Big Data jobs turnaround time through new BeBiDa optimization techniques

The BeBiDa system management tool will enable the effective execution of Big Data jobs upon HPC resources with no interference of typical HPC jobs. This functionality comes with the drawback that in case there is a nearly 100% utilization of the system through the typical HPC workloads then the Big Data jobs will suffer from high turnaround times. To improve this we proposed optimization techniques which make use of simple mechanisms that allow the system to go through the typical HPC usage to get resources which will be used by the Big Data side elastically.

We have implemented the improved BeBiDa guarantees in a way that Big Data jobs can respect deadlines and serve time-critical applications..

#### A) Deadline-aware

In this technique we create empty jobs which do not trigger the prolog/epilog scripts to leave room for Big Data applications to be executed in the space of HPC jobs. The idea is to prepare holes on the HPC schedule plan to guarantee a fixed pool of resources for the Big Data workload.

For that we have set-up a Big Data queue of jobs and when the job queue grows above a certain threshold we submit some HPC jobs with the particular name of <a href="BEBIDA\_NOOP">BEBIDA\_NOOP</a>. which as we also mentioned during the configuration of BeBiDa in the previous section does not remove the Kubernetes node from the available resources hence removing the possibility for HPC jobs to kill the Big Data job which is running on that resource.

For this implementation we have created a new service named "BeBiDa Shaker", hosted on Kubernetes, which has access to the pods list and status. This service looks at new submitted applications and gets the deadline and resource needs using Kubernetes annotations. In particular for Spark applications, these needs are provided as parameters of the Spark driver which demands resources for the spawned Spark executors. Using annotations, the service tries to reserve resources for the application in a way to be sure that it will finish before its deadline. This is done by submitting a HPC job -hence higher priority than the typical Big Data jobs- with prolog and epilog scripts deactivated which will leave the resources for the Big Data workload. In SLURM this has been implemented using the "-begin" parameter. For OAR the advanced reservations functionality has been used to cover this need. This service provides a simple interface to retrieve the following details for each application, its deadline, its estimated resource usage, the associated HPC jobs and the estimated completion time. Figure 14 shows a high-level view of the technique and how the different internal processes are related. In the exceptional case where the deadline cannot be fulfilled an alert is automatically sent to the user by email.

## B) Time-critical

In this technique we make use a dynamic set of resources to serve applications immediately and scale them out and in (grow and shrink) when necessary, inspired by the work of Liu et al<sup>16</sup>.

The technique makes use of the same core mechanisms implemented for Deadline-aware: the "BeBiDa Shaker" service which tracks the submitted Big Data applications on Kubernetes side and if a particular application is labeled as "Time-Critical" then particular resources are taken out of the HPC pool to serve directly the urgent "Time-Critical" demand coming from the Big Data applications. Furthermore this demand can evolve dynamically based on the Big Data application needs.

\_

<sup>&</sup>lt;sup>16</sup> Feng Liu, Kate Keahey, Pierre Riteau, Jon B. Weissman. Dynamically negotiating capacity between on-demand and batch clusters. SC 2018: 38:1-38:11

The implementation of this feature made use of the specific feature of OAR named quotas<sup>17</sup> which allows the administrator to limit the amount of resources used by users or the whole system. In our case we configure it for the whole system. This means that the particular resources will be removed from the typical pool of HPC resources for HPC jobs and will become available as Kubernetes resources to be allocated by the urgent "time-critical" Big Data jobs. The following procedure gives the different steps taking place to address the needs of both "deadline-aware" and "time-critical" techniques of managing elastic Big Data jobs on HPC infrastructures

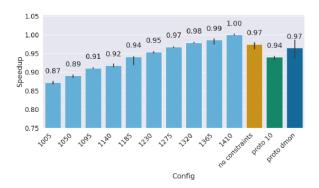

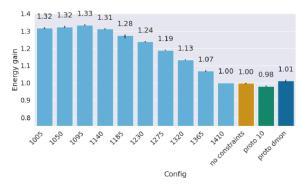

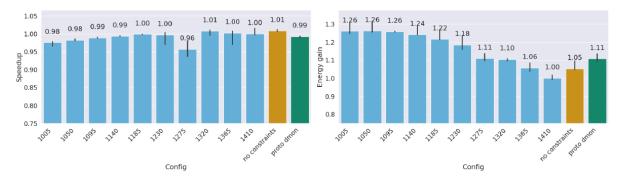

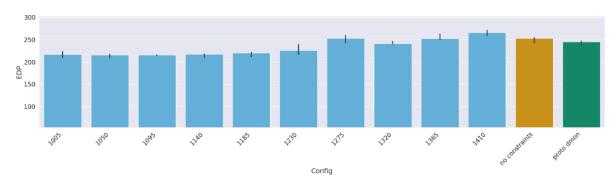

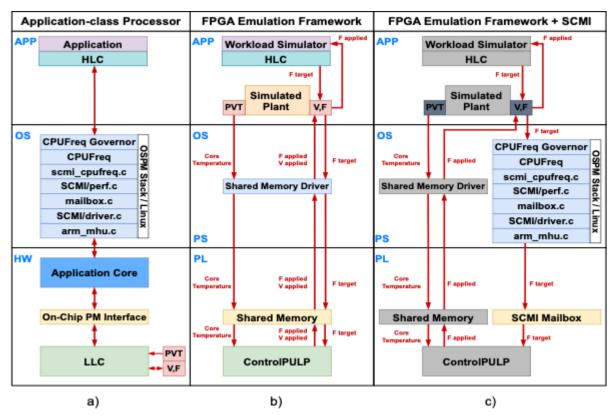

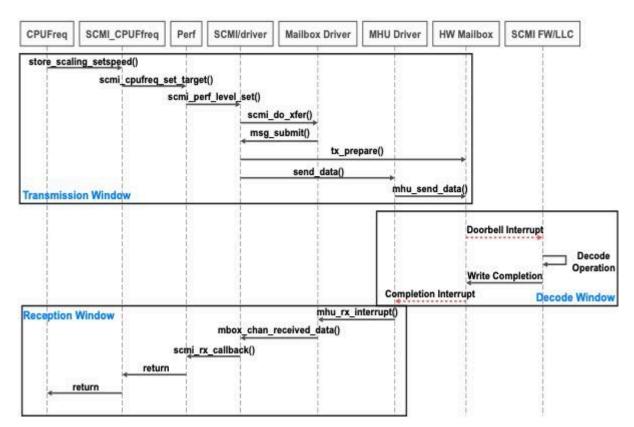

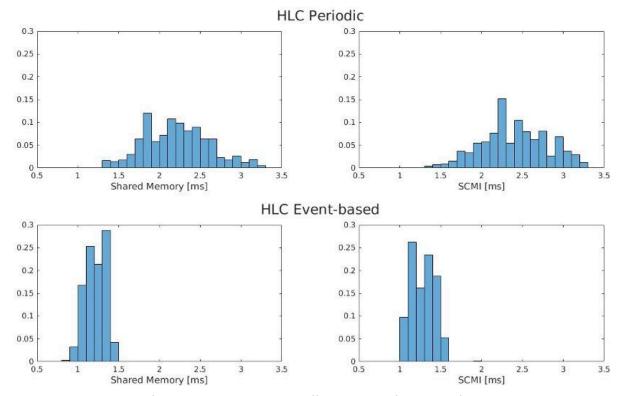

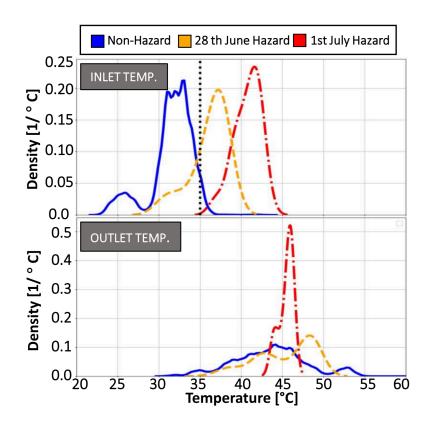

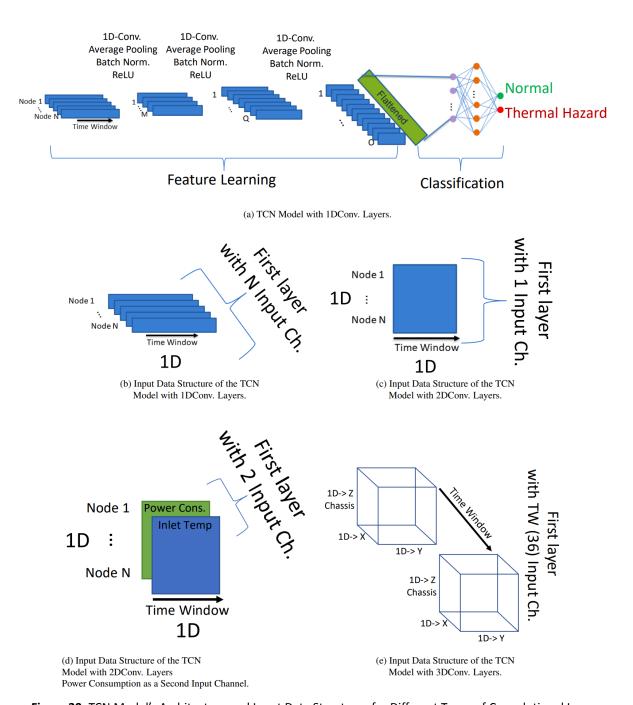

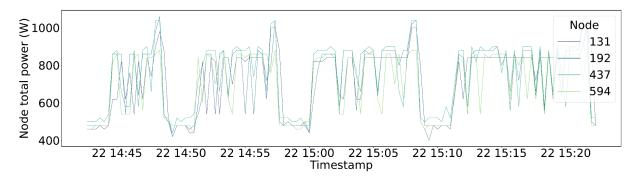

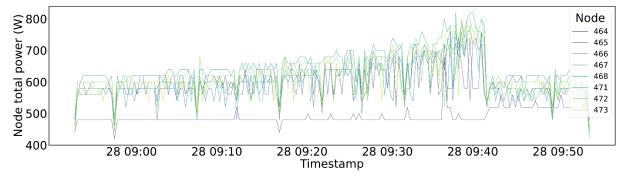

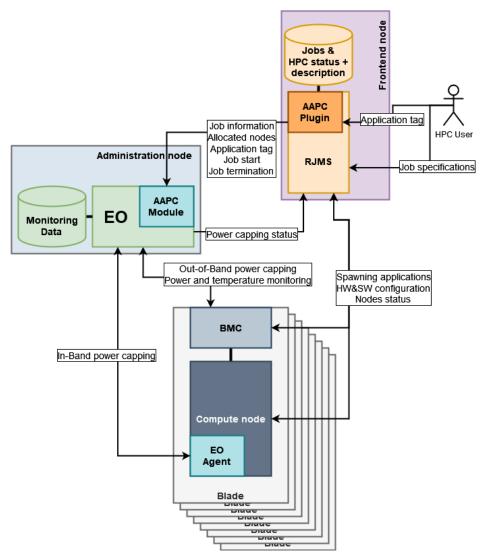

- 1. A user may submit an elastic Big Data (HPDA) application using Kubernetes.